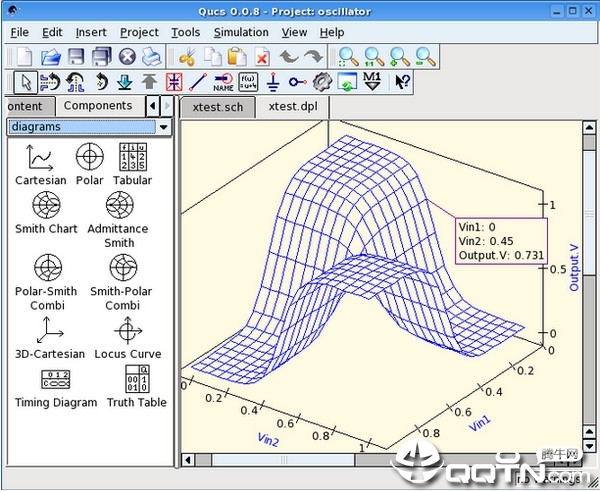

电路模拟器(Qucs)电脑版是一款相当不错的eda仿真软件,Qucs同时也是免费的、开源的电路模拟器,利用这款软件进行模拟,以此测试出各种电路的参数是否正常,它的目的是支持各种电路仿真类型,包括直流,交流, S参数,和谐波平衡分析。

软件功能

如果你想改变的电阻率,然后再切换回您的原理图,通过点击divider.sch选项卡上,按下F4快捷方式,或通过选择仿真→数据显示/原理图菜单项。之后双击R1电阻。

在组件属性“对话框中给定组件的所有属性都可以编辑。一个简短的描述,以及有一个每个属性中显示的复选框可用于添加原理图(或属性名称和值的示意图隐藏它)。允许的属性值元件值标准的(1000),科学(1E - 3)可以选择或工程(1K)数字符号。

节点电压divided.V旁边直流电压,电流通过,源V1.I。数据集列表中只列出项目可投入的图形。可用的数据集项目,根据模拟式用户执行您发现下列类型的在DataSet中的项目。

软件特色

支持对动画电压波形、电流等进行操作

也可对电路的参数进行快速的调整

也支持对控制的按钮进行模拟

也可自动的进行布线

也对示波器进行支持

支持无缝DC、仿真的功能操作

可以对播放、暂停等功能进行控制模拟

也可进行电路原理图的保存、加载

可以对地面建造仿真进行移动

可以对需要的组件进行快速的选择

使用方法

1、打开Qucs,现在Verilog标签下没有任何文件,我们只需要将我们的verilog的.v文件拷贝过来qucs就能自动识别了。

2、一个verilog的半加器代码,这里verilog标签下已经识别到我们的文件了,如果qucs没有刷新在Projects下重新点击一下工程的名字就能看到文件添加过来了。

3、然后鼠标点击一下这个main.v,之后鼠标移到我们的原理图上就会出现一个子电路,四个端口,和我们程序里的两个输入两个输出一致。 qucs非常漂亮!

4、然后我们进行一个数字的仿真

5、注意,在digital simulation中我们需要将model的值修改为verilog,因为还有一个选项是VHDL,所以理论上VHDL的代码也能仿真。

6、点击OK之后我们就算做好工作了,然后仿真一下,用真值表显示一下我们的半加器是否正确。

配置需求

源建设要求:

Linux、MacOS、Windows、FreeBSD

Qt4安装版> = 4.6(与 qt3support)

C++编译器

autoconf版本2.64(至少)

GNU automake 1.7.0(至少)

Flex 2.5.31(但至少2.5.9)

GNU的野牛1.875d

GNU M4(任何版本)

GNU gperf 3.0.1

ADMS 2.3.6

[b2_file link="https://www.qqtn.com/down/457405.html" name="eda仿真软件-电路模拟器(Qucs)0.029 免费版" pass="" code=""]